The IIS Chip Gallery

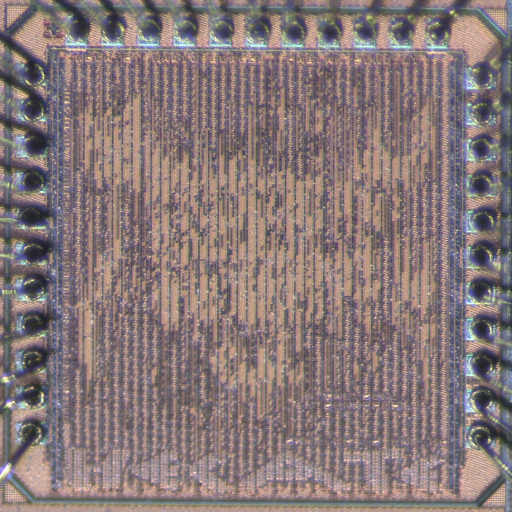

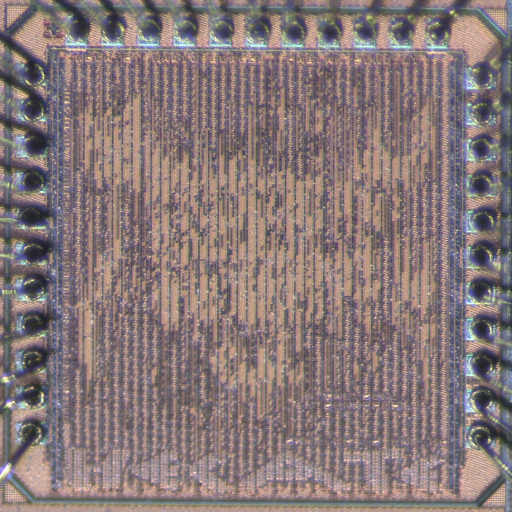

Hecate (2014)

Additional pictures below, click to see larger versions

by

| Application | Pulp |

| Technology | 65 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | QFN40 |

| Dimensions | 1252μm x 1252μm |

| Gates | 600 kGE |

| Voltage | 1.2 V |

| Power | 1 mW @1.2V 1MHz |

| Clock | 500 MHz |

This is one of a series of four chips that is part of the PULP project which add various floating point operations to a cluster of 4 processors.

All four chips use the same basic PULP architecture with 4 Or10n cores, 16 kBytes of L2 memory, 16 kBytes of TCDM memory organized into 8 banks and a total of 4 kBytes of instruction cache. The difference is how the floating point units are added to the system.

In a normal multi-core system, the probability that all cores simultaneously utilize the FPU is relatively low. Instead of adding a dedicated FPU core, a smaller number of cores could theoretically be shared between a larger number of CPUs. Hecate, implements such a system, where the four cores share 2 FPUs. The FPUs are identical to those designed in Artemis. As these do not contain a dedicated divider, the area gain is minimal. However, this architecture is beneficial when the FPU is larger, such as the LNS FPU used in Selene.

The names have been chosen from the mythology. In Greek mythology Hecate, among other things, is associated with crossroads. This is fitting for this chip, as it introduces an interconnect that provides a sort of crossroads for flotaing point data in the PULP system.