The IIS Chip Gallery

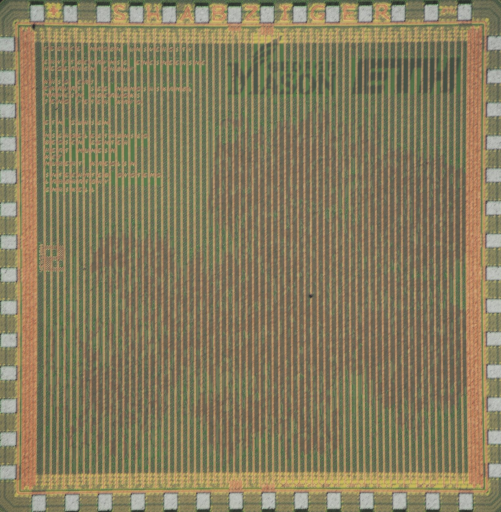

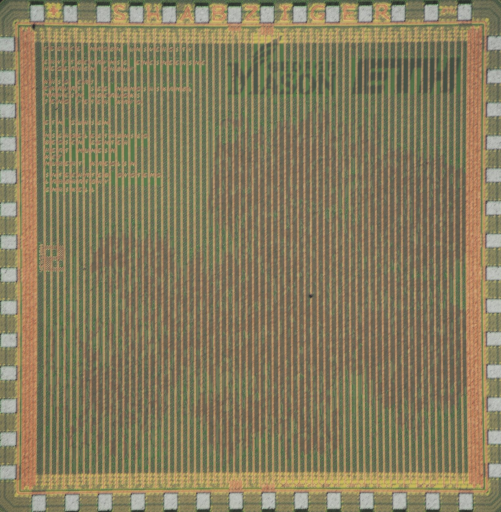

Shabziger (2011)

by

| Application | Cryptography |

| Technology | 65 |

| Manufacturer | UMC |

| Type | Research Project |

| Package | QFN56 |

| Dimensions | 1875μm x 1875μm |

| Gates | 1200 kGE |

| Voltage | 1.2 V |

| Power | mW |

| Clock | 200-600 MHz |

Shabziger contains the Secure Hash Algorithm-3 (SHA3) 3rd round candidates: Blake, Groestl, JH, Keccak, Skein and a SHA2 implementation from two sources. Area per throughput optimized versions are provided by the Cryptographic Engineering Research Group (CERG) of the George Mason University, the ETH provided versions optimized for a pre-set throughput rate of 2.488 Gbps (the payload of a OC-48 frame)

All sources for this chip are available under Our SHA-3 Page.

The name Shabziger is a play on the SHA algorithm and a local cheese type called 'Schabziger' from the Glarus region. Traditionally the Microelectronics Design Center names its chips after Swiss Cheese (see Sbrinz for example).