The IIS Chip Gallery

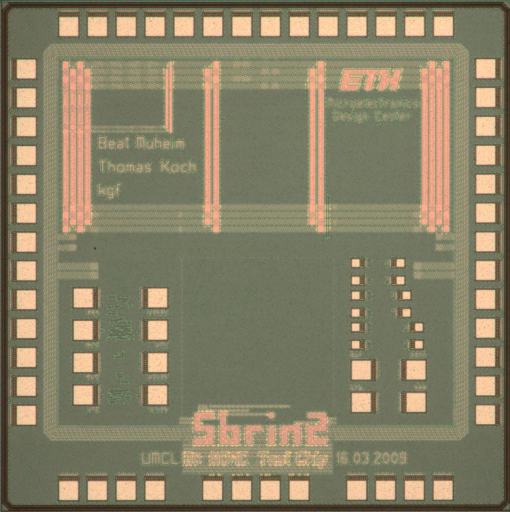

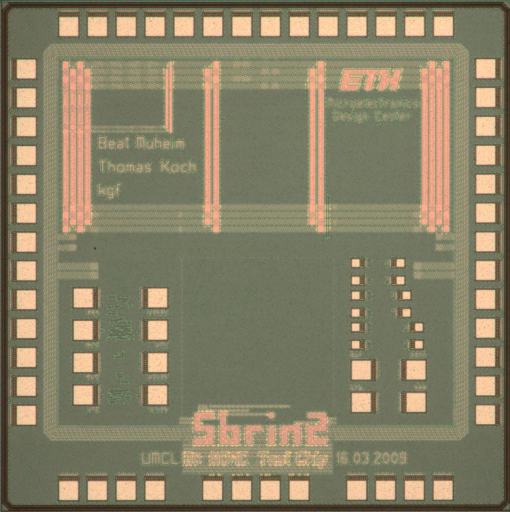

Sbrinz (2009)

by

| Application | Test |

| Technology | 130 |

| Manufacturer | UMC |

| Type | Test Chip |

| Package | QFN56 |

| Dimensions | 1525μm x 1525μm |

| Gates | 50 kGE |

| Voltage | 1.2 V |

| Clock | 30-600 MHz |

Test chip for the Microelectronics Design Center. Contains the following main blocks: