The IIS Chip Gallery

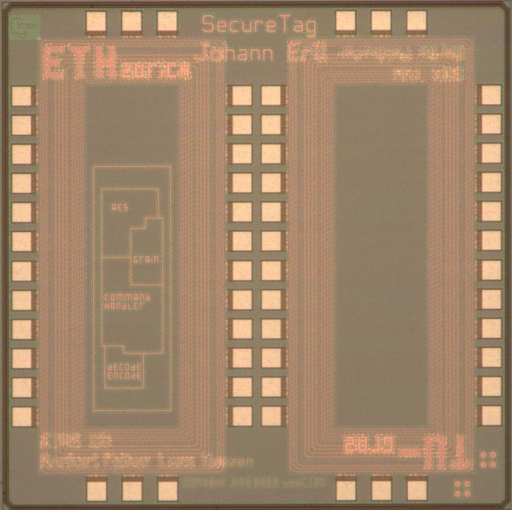

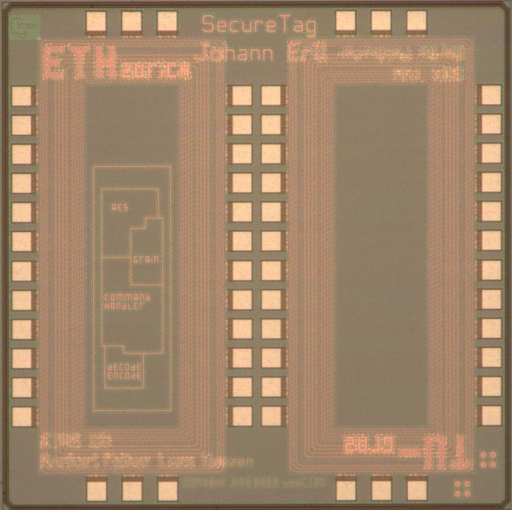

SecureTag (2009)

by

| Application | Cryptography |

| Technology | 130 |

| Manufacturer | UMC |

| Type | Diploma Thesis |

| Package | QFN48 |

| Dimensions | 1525μm x 700μm |

| Gates | 14 kGE |

| Voltage | 1.2 V |

| Power | 0.005 mW |

| Clock | 3.5 MHz |

Radio Frequency identification (RFID) tags consist of an integrated circuit (IC) attached to an antenna. The IC combines an analog frontend, a digital controller for the protocol handling, nonvolatile memory for electronic product code (EPC) and password storage, and possibly modules for cryptographic protocols. This work implemented the digital part of the EPC standard compliant tag, extended by cryptographic units in order to implement an authentication protocol.

Since the VLSI process for student projects does not support nonvolatile memory, a test interface has been realized which allows direct access for the initialization of all memories and separate control of the AES and Grain cryptographic modules. The main parts of the device are the controller for the protocol handling, the en/decoder for the data to and from the RF interface, a Grain stream cipher used to generate secure (pseudo) random numbers for the challenge response protocol and an ecryption-only AES core.

Special attention was out on enhanced resistance against cryptographic DPA attacks by use of a sophisticated clocking strategy which is also responsible for reaching low power consumption. The power overhead could be limited to less than 0.2uW of the total 4.8uW and a silicon overhead of less than 1'000 gate equivalents out of a total of 13'000.

The chip has two different variations, due to the small size these have been manufactured on the same 1.525 x 1.525 mm2 die. The two chips are rotation symmetric and share the same bonding diagram.

This chip is one of the long series of ASICs that was manufactured in collaboration with the IAIK of TU-Graz.