The IIS Chip Gallery

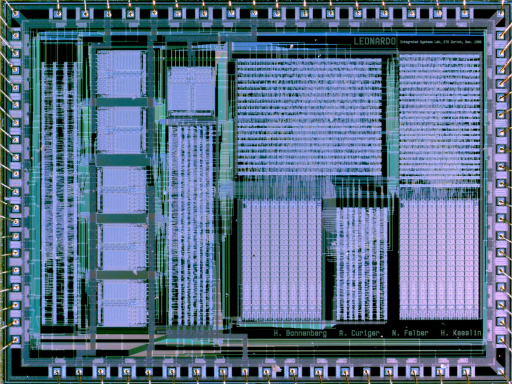

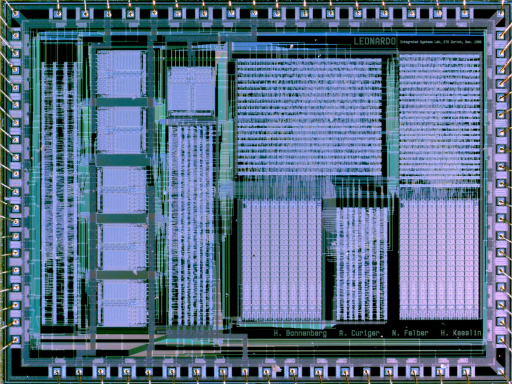

Leonardo (1990)

Additional pictures below, click to see larger versions

by

| Application | Cryptography |

| Technology | 1500 |

| Manufacturer | VLSI Tech |

| Type | Research |

| Package | PGA84 |

| Dimensions | 9300μm x 7000μm |

| Gates | 30 kGE |

| Voltage | 5 V |

| Power | 1000 mW |

| Clock | 33 MHz |

At the IS, a new 64-bit block cipher algorithm has been developed. the cipher is based on mixing of operations in different algebraic structures and is proposed to become a new European encryption standard. In a very early stage of development hardware implementation aspects have been taken into consideration and have significantly influenced the cipher.

To achieve a high data encryption rate, the chip's datapth is strongly pipelined. By the use of a highly sophisticated data scheduling scheme it is guaranteed that the pipeline is permanently fully loaded. A data encrytpion rate of 44 Mbit/s is achieved with a 25 MHz chip clock. To provide the pipeline with a sufficient amount of data an extremely fast interface is required. Hence a 32-bit parallel interface was implemented permitting data rate of up to 33 MByte/s.

The chip design is cell based. The 95'000 transistors including one Kbit of RAM and two 17x17 bit multiplier macrocells, indicate the high complexity of the chip.