The IIS Chip Gallery

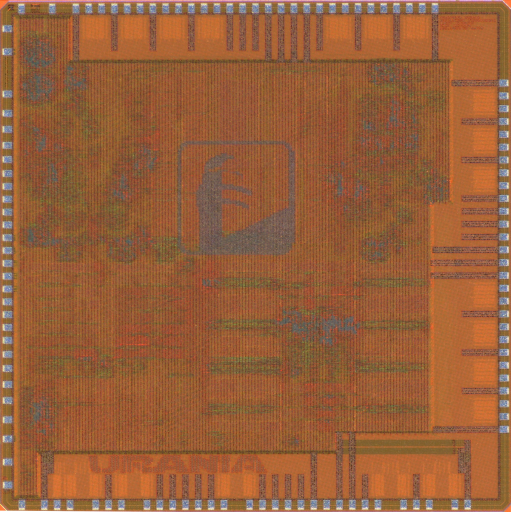

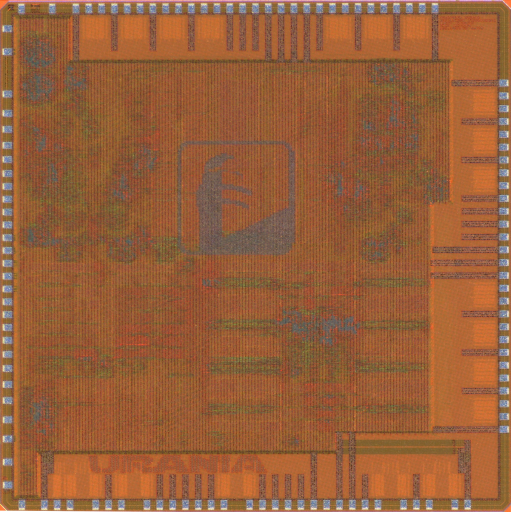

Urania (2019)

Additional pictures below, click to see larger versions

by

| Application | Pulp |

| Technology | 65 |

| Manufacturer | UMC |

| Type | Research |

| Package | QFN64 |

| Dimensions | 4000μm x 4000μm |

| Gates | 6 MGE |

| Voltage | 1.2 V |

| Power | 1 pW @1.2 V, 1 GHz mW |

| Clock | 100 MHz |

Urania is the first ASIC implementation of the bigPULP architecture used mainly for our HERO project. Unlike the HERO implementations that run on Xilinx SoC platforms, Urania is a completely RISC-V based heterogeneous system that contains a 64bit Ariane core as the main host processor and two clusters with each four RI5CY cores with individual transprecision enabled FPUs.

Each cluster contains PULPo, a specialized hardware accelerator for first order optimization methods that solve a wide range of problems (such as L1-norm minimization and non-negative least squares), developed by the VLSI Information Processing (VIP) group at Cornell University.

The chip also contains a DDR3 interface designed by Division of Microelectronic System Design of TU-Kaiserslautern as part of our collaboration in the OPRECOMP H2020 project.

Urania is one of the nine muses of the Greek mythology in the domain of Astronomy. Urania is also the name of a prominent observatory in downtown Zurich. The small logo on the chip references this observatory.