The IIS Chip Gallery

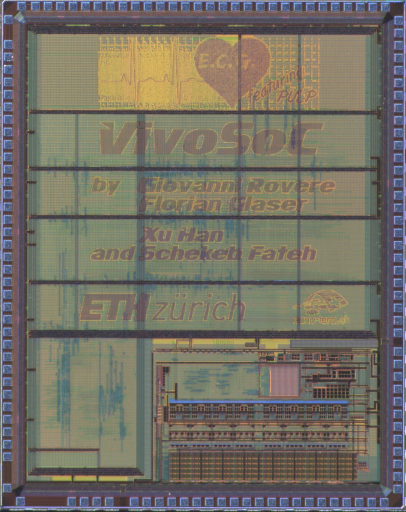

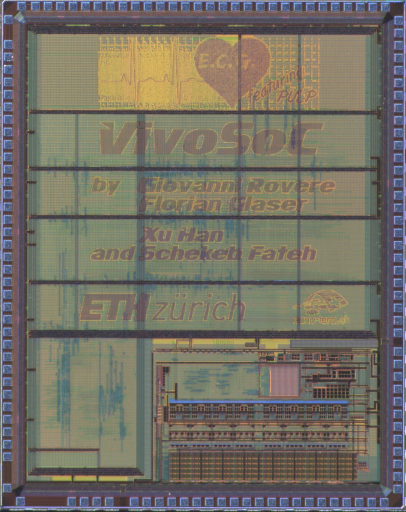

Vivosoc (2015)

Additional pictures below, click to see larger versions

by

| Application | Processor |

| Technology | 130 |

| Manufacturer | SMIC |

| Type | Research |

| Package | Baredie |

| Dimensions | 4000μm x 3200μm |

| Gates | 600 kGE |

| Voltage | 1.2 V |

| Power | 45 mW (@40MHz, 1.2V) |

| Clock | 140 MHz |

The VivoSoC is a chip the combines a very flexible analog acquisition circuitry and SAR-ADC with a Parallel Ultra Low Power processor (PULP) This is meant to be used for biomedical signal acquisition, such as EEG, ECG and EMG in a wearable context. The Analog Front End (AFE) design is based on the chip CerebroV4.1 Jack while the processor is based on PULP v2 design with the addition of a peripheral block that configures and reads out data from the AFE.

Main chip features:

The name VivoSoC is based on the Italian word "Vivo" that can be translated as "Alive".

A newer version of this chip is VivoSoc2