The IIS Chip Gallery

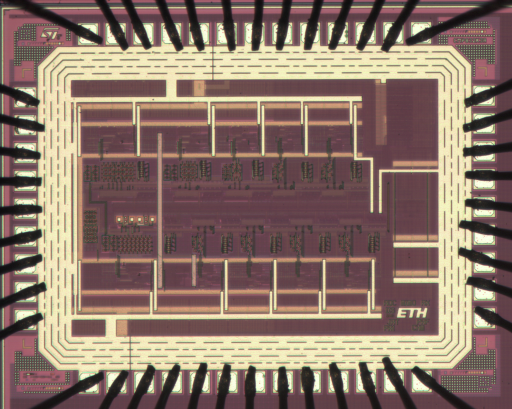

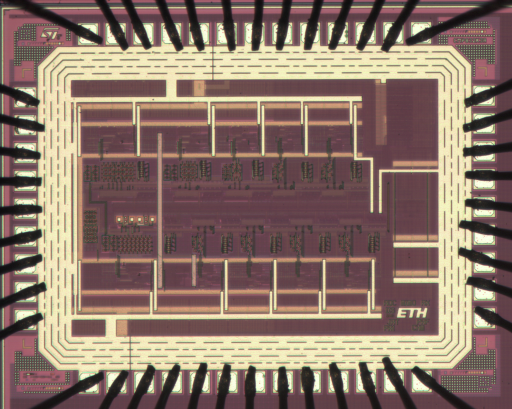

MIMO_RX (2003)

by

| Application | Converter |

| Technology | 180 |

| Manufacturer | STM |

| Type | Diploma Thesis |

| Package | LCC44 |

| Voltage | 1.8 V |

| Power | 70 mW, 1.8V, 100MHz |

| Clock | 25 MHz |

The pipeline A/D converter is one of the preferred solutions for industrial applications requiring high conversion rate and moderate accuracy. A popular architecture adopts 1.5bits per stage. The fundamental limitation of this circuit type lies in the limited accuracy of reasonably sized capacitors implemented in current CMOS technologies. Recently, a capacitor mismatch shaping technique has been proposed and demonstrated which is able to improve the ADC accuracy at the expense of a slightly expanded bandwidth. This technique is of interest since in practice a moderate oversampling ratio is always welcome in order to relax the specifications of the analog anti-aliasing filter at the ADC input, and since the shaped noise can easily be removed by the subsequent digital filtering.

The project has used this technique for the first time in a 1.5bit-per-stage architecture. The measured results of a prototype chip are very encouraging. The SFDR improves by more than 10dB when the mismatch shaping is activated. The circuit implemented in 0.18um CMOS consumes 70mW at 1.8V and 100MHz update rate. The measured SFDR is >60dB and the SNR is above 55dB for OSR=4.