The IIS Chip Gallery

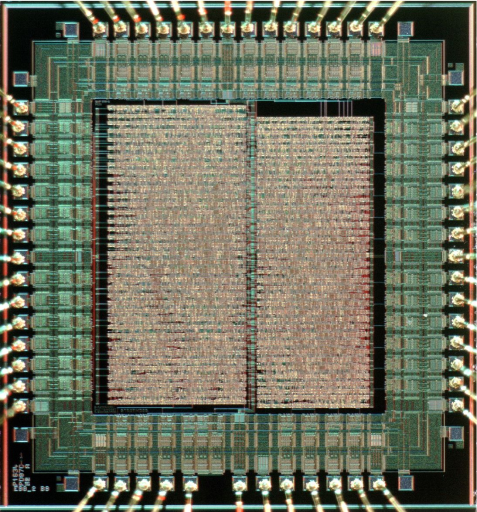

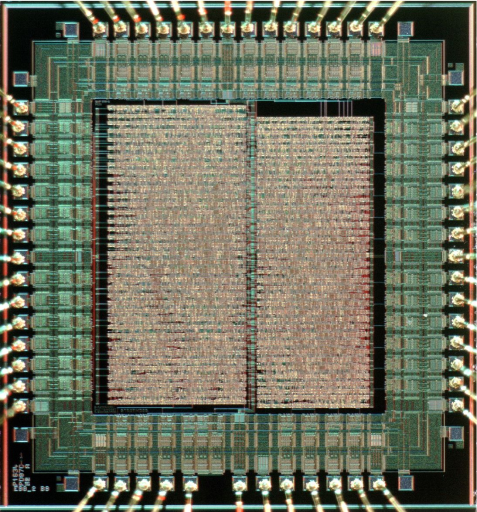

3DES (1998)

by

| Application | Cryptography |

| Technology | 800 |

| Manufacturer | ES2 |

| Type | Semester Thesis |

| Package | LCC64 |

| Voltage | 5 V |

| Clock | 50 MHz |

DES (Data Encryption Standard) is a 64-bit block cipher with 56 bits key length. Its security is enhanced in the Triple-DES algorithm, where three encryptions are applied in series using a key of 112 bits.

In this work, two ASIC cores for DES and Triple-DES have been developed. The DES Engine core combines single and triple operation, performing one encryption round per clock cycle (DES requires totally 16 rounds). The System DES core only implements triple operation, but performs two encryption rounds per clock cycle, resulting in a higher throughput. The cores include the encryption data path, the key scheduler, and a controller.

The two cores have been realized in synthesizable VHDL code for easy integration as coprocessors into an ASIC. In a 0.6 mm 3 V standardcell technology, the DES Engine counts about 5k gates and achieves 120 Mbit/s data rate at 90 MHz, while System DES counts 8k gates and delivers 128 Mbit/s at 50 MHz (both in Triple-DES mode).

In addition, a Stream DES ASIC has been integrated. It incorporates the DES Engine as core together with an 8-bit interface and implements the ECB and CFB ciphering modes. It was fabricated in an 0.8 mm process and was successfully tested up to 50 MHz, delivering 177 Mbit/s data rate (in DES mode).